March 16, 2016

Toyota - 10-14-2015, 10:39 PM

Vpecker can do injector coding for a part of Toyota models.

I have tested and compared today vpecker and launch iscan on Mazda 6 GH 2.0 diesel 2008 year.

tested with vpecker ver.6.3

BMW 530d E60 engine connect , but only read/erase fault code and live data ,service reset

I have tried today on VW Golf MK IV 1.9 tdi, haves a lot of functions, this time even more than launch idiag, it haves even guided function, and a lot special functions,and login,taht is the first that vpecker works even better...

I have tested today on ASTRA J 2011 1.7 cdti works ok,has special functions not a lot but ok.

But it works until 2011

Tested today on Kia Cerato petrol,and finally some result, it haves options like launch idiag only one function is not there and that is brake fluid bleeding,all the reset functions are the same.

So far all cars that i have tested this one is the first one that haves some extra functions...

Opel Astra G 1.4 twinport (Z14XEP) engine no connection

Opel Vectra GTS 2.0T engine (trionic

I have bought and installed on windows 8.1 tablet. Can’t connect or read any bmw 330ci ecu. Event not recognise any module. tried on an e39 530i but alsocouldn’t recognise any ecu...

Posted by: OBDexpress.co.uk at

08:24 AM

| No Comments

| Add Comment

Post contains 386 words, total size 4 kb.

March 15, 2016

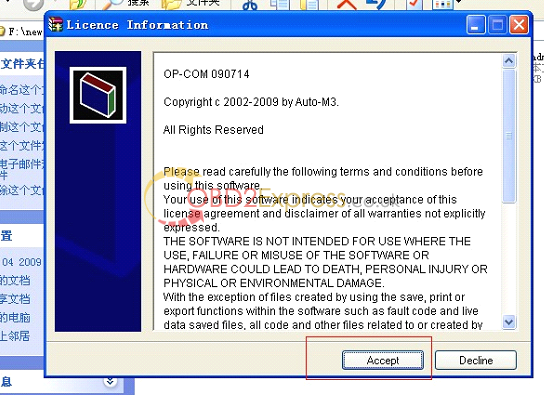

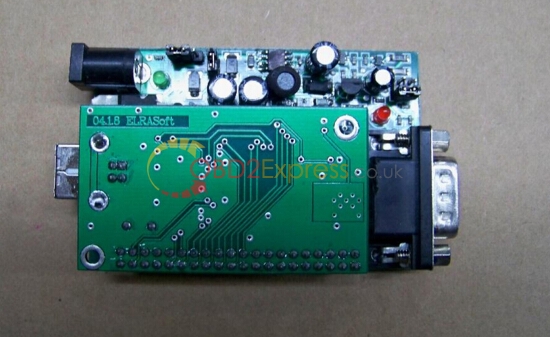

Here is the step-by-step instruction on how to setup Firmware 1.59 Opcom OP-Com 2012V software.

Software: V2012

Firmware: V1.59

Language: English. (If you need german, please choose SP12 OPCOM German version.)

How to setup Firmware 1.59 Opcom OP-Com 2012V software:

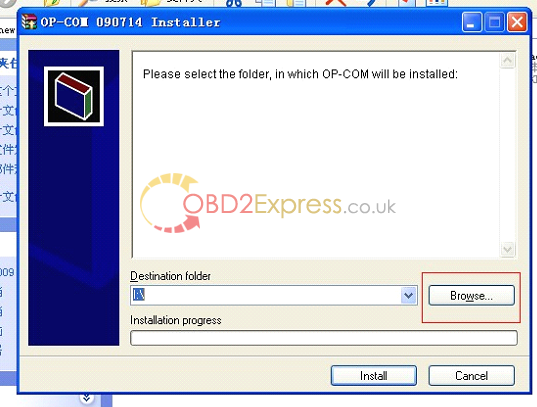

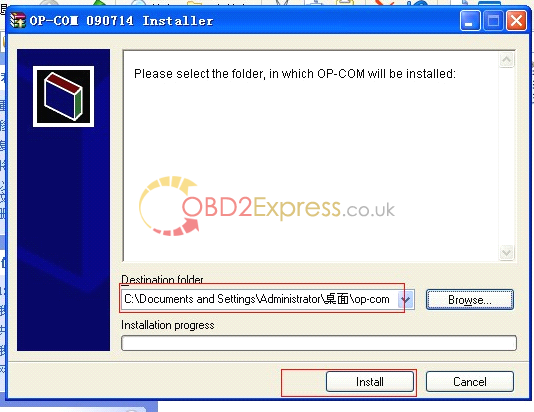

1.create a folder named [op-com] at the desktop.

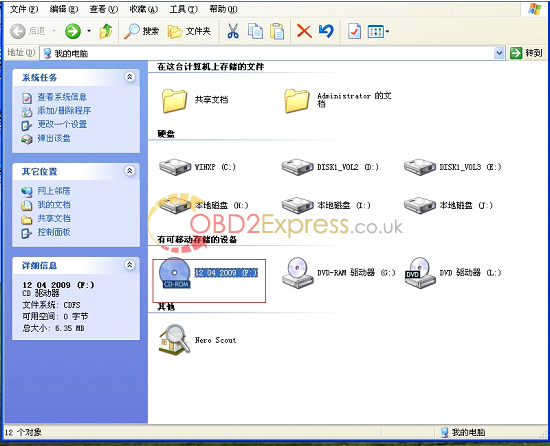

2.open [op-com] CD.

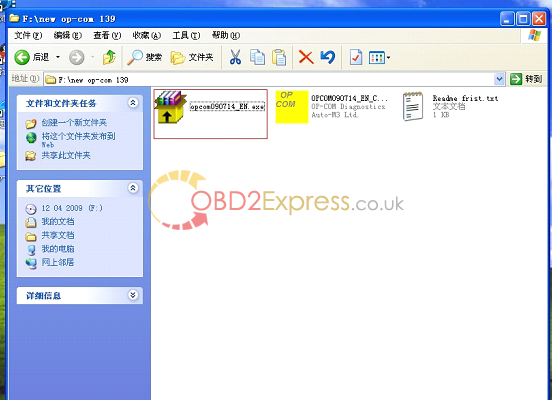

3.set up "op-com EN exeâ€.

4. Destination folder (Please select the folder, in which OP-COM will be installed), here you select the blank folder "op-com†you just now created in the desktop.

5.open "op-com†folder in your desktop.

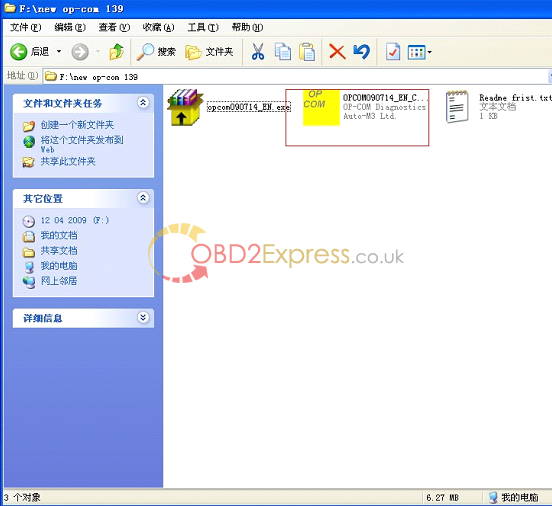

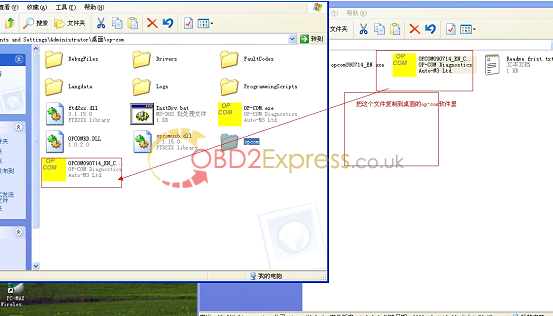

6. Open the CD and copy the "OPCOM090714_EN_Crack.exeâ€, then paste them into the folder of "op-com†in the desktop.

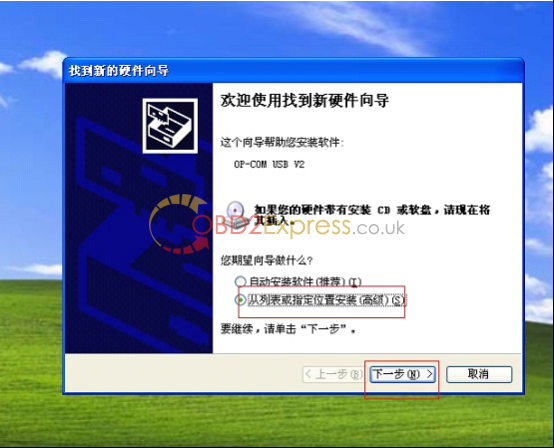

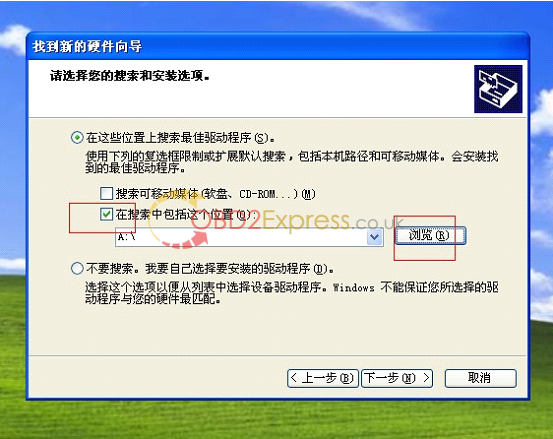

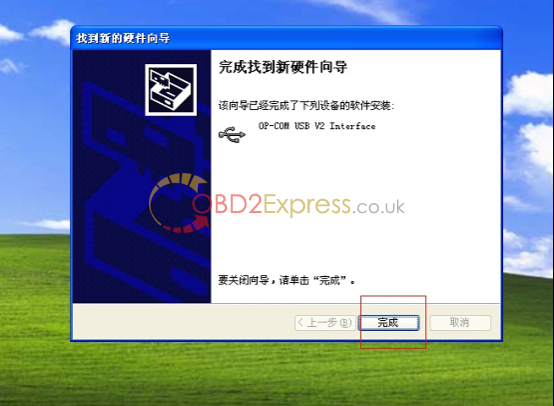

7 .connect op-com interfaces to your PC, then it will tell you to setup op-com driver, please select the second option and click "Nextâ€.

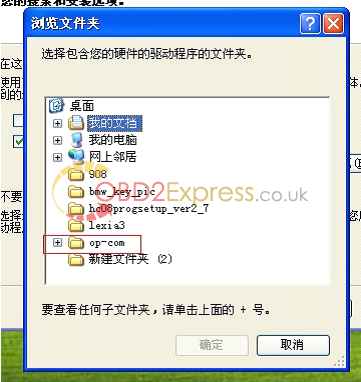

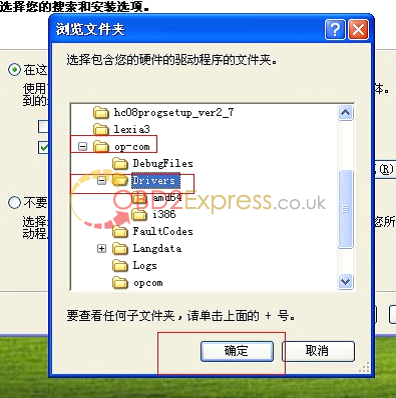

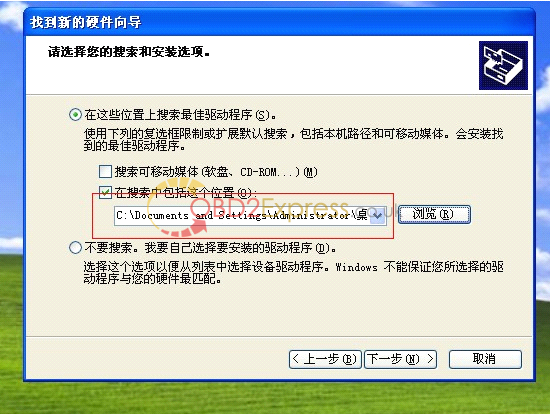

8, select the destination folder for driver setup.

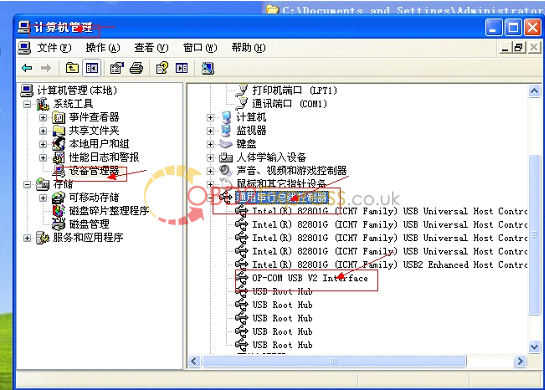

9. finish setup driver, now check op-com driver location "My computer=management= device management=USBâ€, if op-com driver location shows as follows, that means it is ok now.

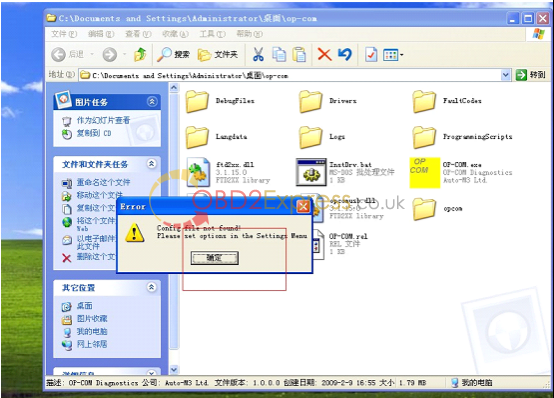

10. Open "OPCOM090714_EN_Crack.exe†under the folder of "op-com†on the desktop, ready to activate software. Com not found, because the software is not activated.

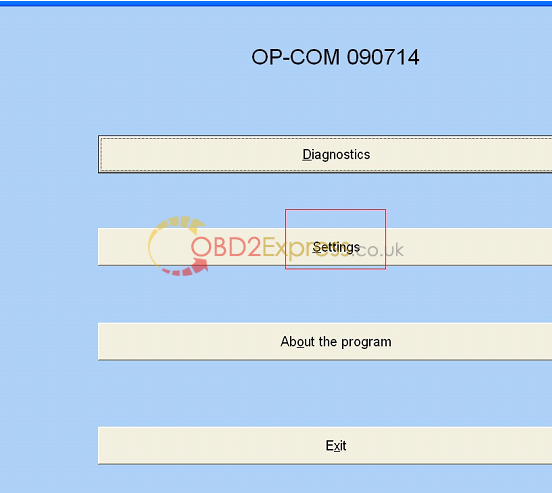

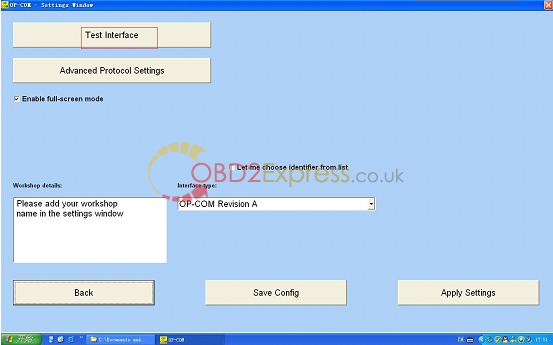

11.Click "Settingsâ€.

12.Click "test interfaceâ€, run activation program.

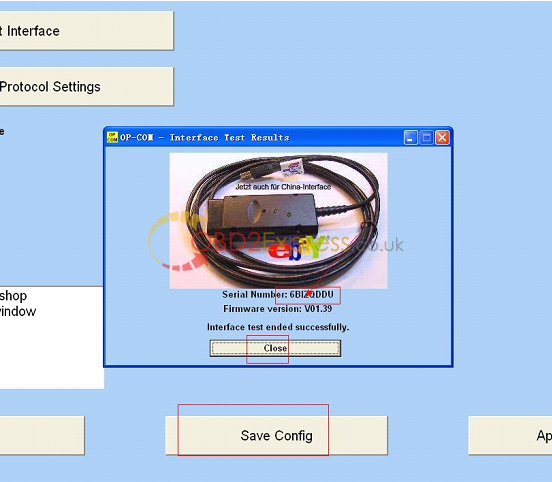

13.activation program runs well and get Serial Number, "Save Configâ€, "close†Serial Number.

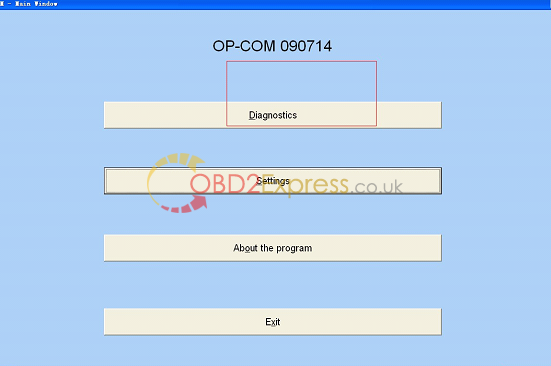

14.Select "diagnosticsâ€.

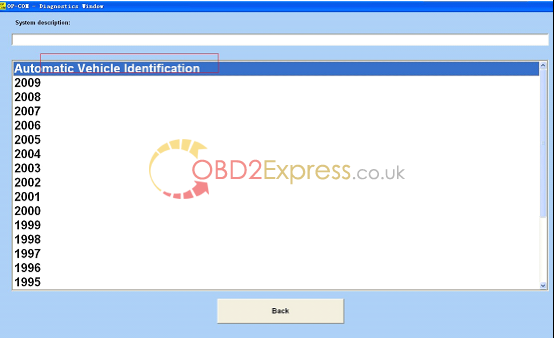

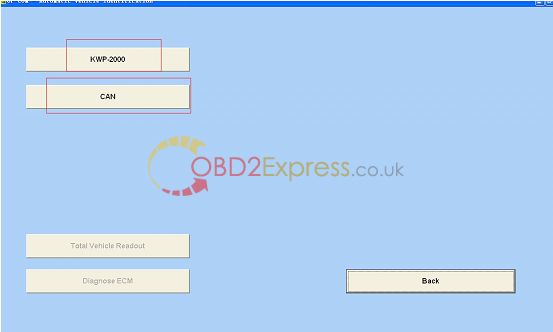

15.select protocol to diagnosis.

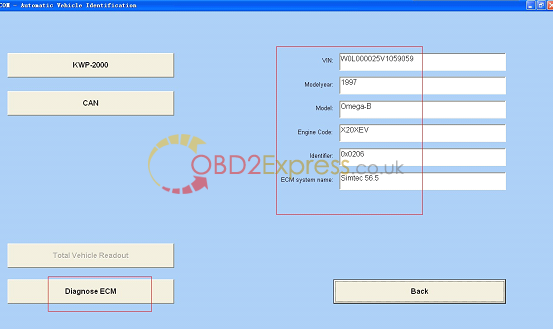

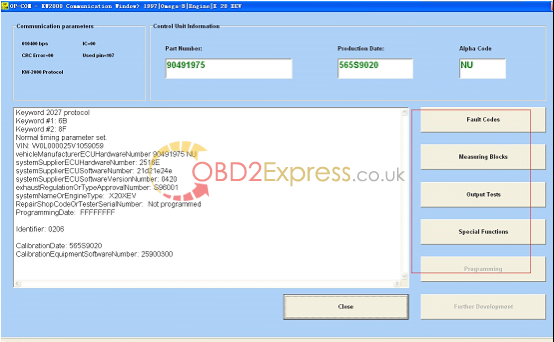

16.pass the protocol, select "diagnose ECMâ€.

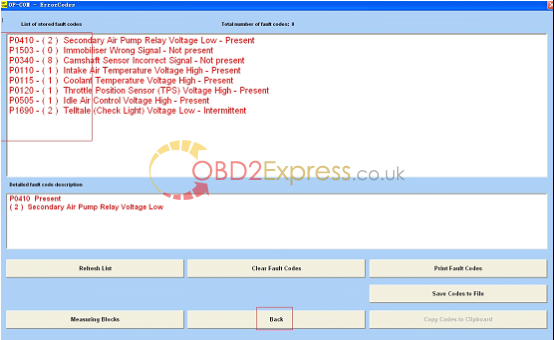

17.Read fault codes.

More information:http://www.obdexpress.co.uk/wholesale/opcom-op-com-2010-v-can-obd2-opel-obd2express.html

Posted by: OBDexpress.co.uk at

03:58 AM

| No Comments

| Add Comment

Post contains 233 words, total size 8 kb.

March 14, 2016

VAG VVDI software has been updated, the latest version is V3.5.3, this article is to show you the VAG VVDI all software free download.

Latest Version: V3.5.3

Language: English only.

Update Online

Notes:

Before setup the device software, please disable/uninstall anti-virus software

More information:http://www.obdexpress.co.uk/wholesale/vvdi-china-vag-vehicle-diagnostic-interface.html

Posted by: OBDexpress.co.uk at

06:38 AM

| No Comments

| Add Comment

Post contains 156 words, total size 3 kb.

March 07, 2016

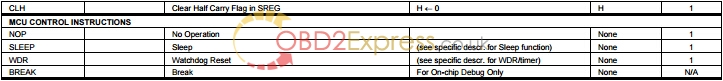

This is the user manual of

Main parts in the manual:

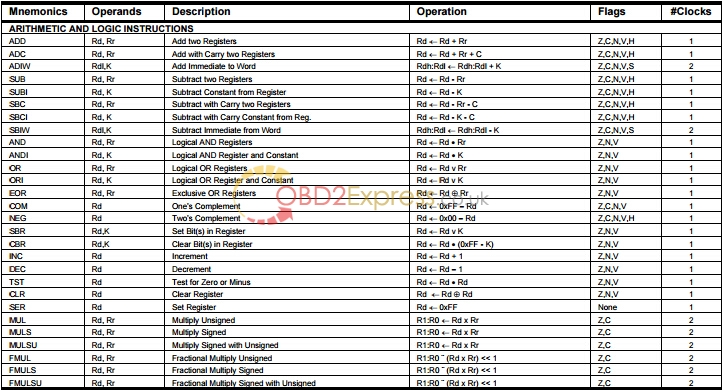

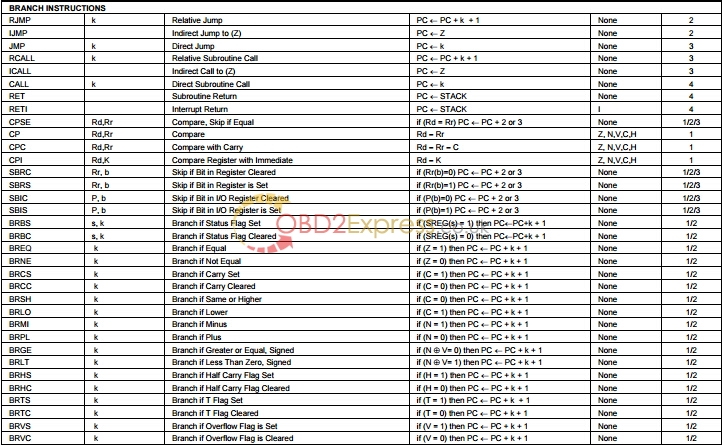

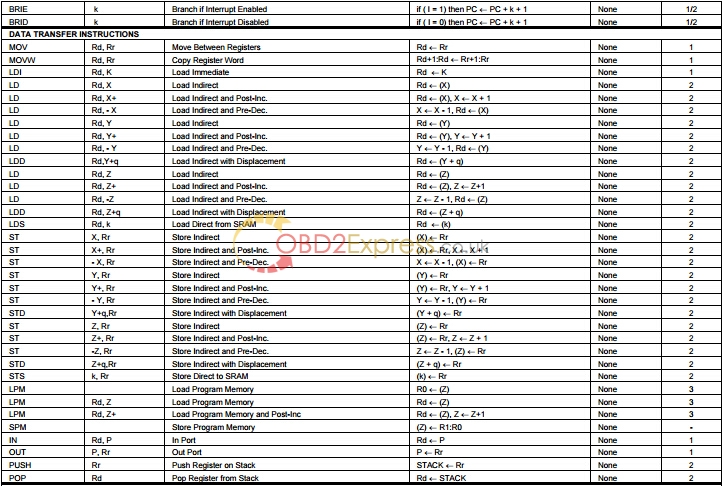

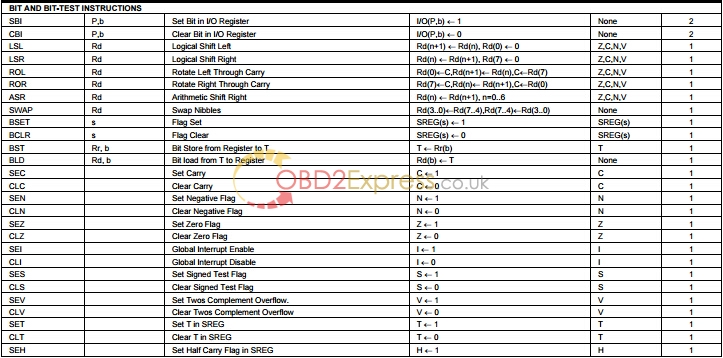

ATmega103 and ATmega64 Compatibility

• High-performance, Low-power AVR® 8-bit Microcontroller

• Advanced RISC Architecture

– 130 Powerful Instructions – Most Single Clock Cycle Execution

– 32 x 8 General Purpose Working Registers + Peripheral Control Registers

– Fully Static Operation

– Up to 16 MIPS Throughput at 16 MHz

– On-chip 2-cycle Multiplier

• Non-volatile Program and Data Memories

– 64K Bytes of In-System Reprogrammable Flash

Endurance: 10,000 Write/Erase Cycles

– Optional Boot Code Section with Independent Lock Bits

In-System Programming by On-chip Boot Program

True Read-While-Write Operation

– 2K Bytes EEPROM

Endurance: 100,000 Write/Erase Cycles

– 4K Bytes Internal SRAM

– Up to 64K Bytes Optional External Memory Space

– Programming Lock for Software Security

– SPI Interface for In-System Programming

• JTAG (IEEE std. 1149.1 Compliant) Interface

– Boundary-scan Capabilities According to the JTAG Standard

– Extensive On-chip Debug Support

– Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

• Peripheral Features

– Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes

– Two Expanded 16-bit Timer/Counters with Separate Prescaler, Compare Mode, and Capture Mode

– Real Time Counter with Separate Oscillator

– Two 8-bit PWM Channels

– 6 PWM Channels with Programmable Resolution from 1 to 16 Bits

– 8-channel, 10-bit ADC

8 Single-ended Channels

7 Differential Channels

2 Differential Channels with Programmable Gain (1x, 10x, 200x)

– Byte-oriented Two-wire Serial Interface

– Dual Programmable Serial USARTs

– Master/Slave SPI Serial Interface

– Programmable Watchdog Timer with On-chip Oscillator

– On-chip Analog Comparator

• Special Microcontroller Features

– Power-on Reset and Programmable Brown-out Detection

– Internal Calibrated RC Oscillator

– External and Internal Interrupt Sources

– Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby and Extended Standby

– Software Selectable Clock Frequency

– ATmega103 Compatibility Mode Selected by a Fuse

– Global Pull-up Disable

• I/O and Packages

– 53 Programmable I/O Lines

– 64-lead TQFP and 64-pad MLF

• Operating Voltages

– 2.7 - 5.5V for ATmega64L

– 4.5 - 5.5V for ATmega64

• Speed Grades

– 0 - 8 MHz for ATmega64L

– 0 - 16 MHz for ATmega64

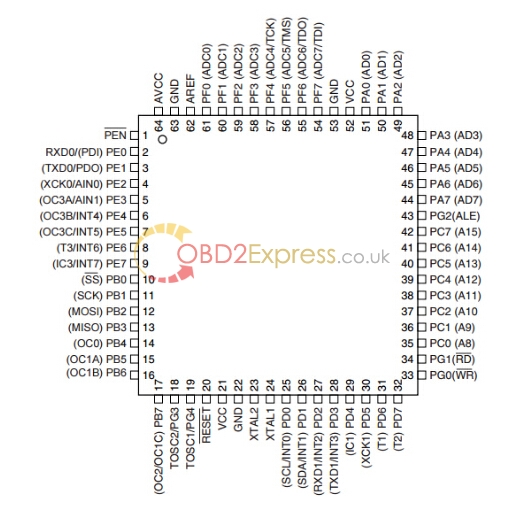

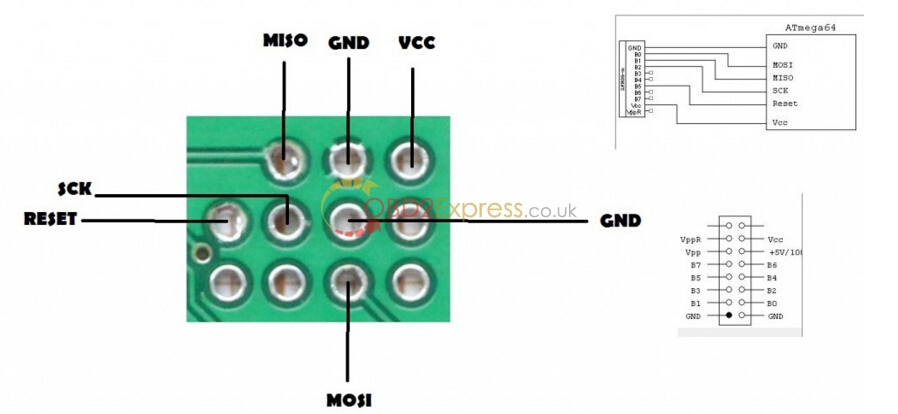

ATMEGA64 update chip pinout

ATMEGA64 for Xprog M ECU programmerpinout:

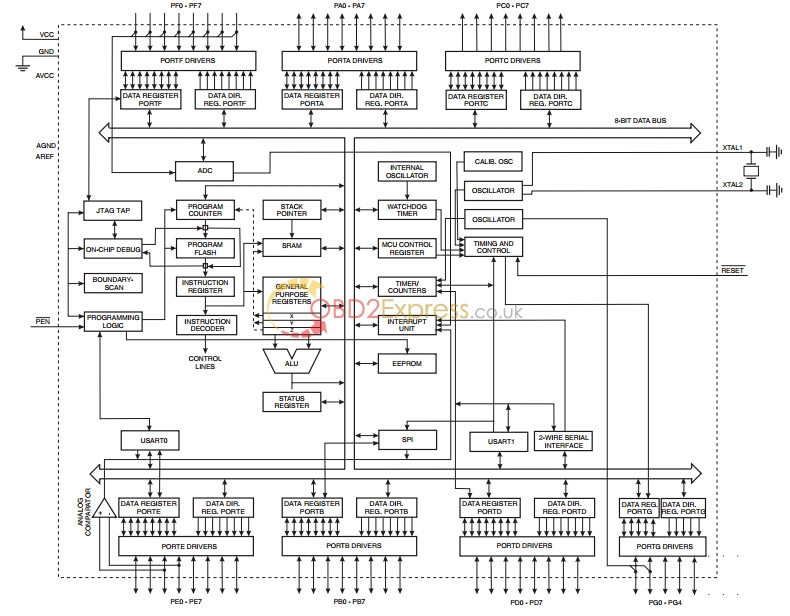

Block Diagram

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega64 provides the following features: 64K bytes of In-System Programmable Flash with Read-While-Write capabilities, 2K bytes EEPROM, 4K bytes SRAM, 53 general purpose I/O lines, 32 general purpose working registers, Real Time Counter (RTC), four flexible Timer/Counters with compare modes and PWM, two USARTs, a byte oriented Two-wire Serial Interface, an 8-channel, 10-bit ADC with optional differential inputstage with programmable gain, programmable Watchdog Timer with internal Oscillator,an SPI serial port, IEEE std. 1149.1 compliant JTAG test interface, also used for accessing the On-chip Debug system and programming, and six software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM,Timer/Counters, SPI port, and interrupt system to continue functioning. The Powerdown mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or Hardware Reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except asynchronous timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low power consumption. In Extended Standby mode, both the main Oscillator and the asynchronous timer continue to run.

The device is manufactured using Atmel’s high-density non-volatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed In-System through an SPI serial interface, by a conventional non-volatile memory programmer, or by an On-chip Boot program running on the AVR core. The Boot Program can use any interface to download the Application Program in the Application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section isupdated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega64 is a powerful microcontroller that provides a highly-flexible and cost-effective solution to many embedded control applications.

The ATmega64 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, In-Circuit Emulators, and evaluation kits.

ATmega103 and ATmega64 Compatibility

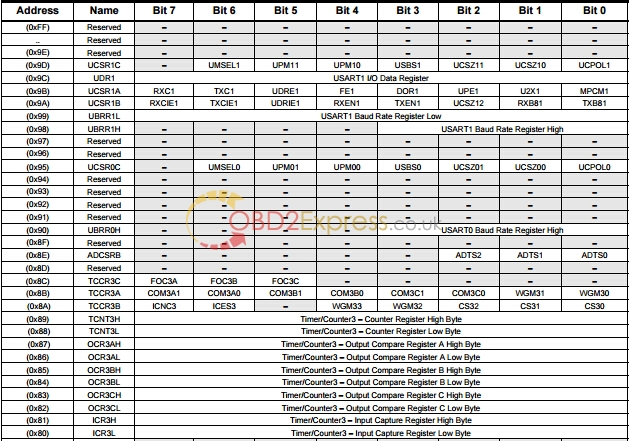

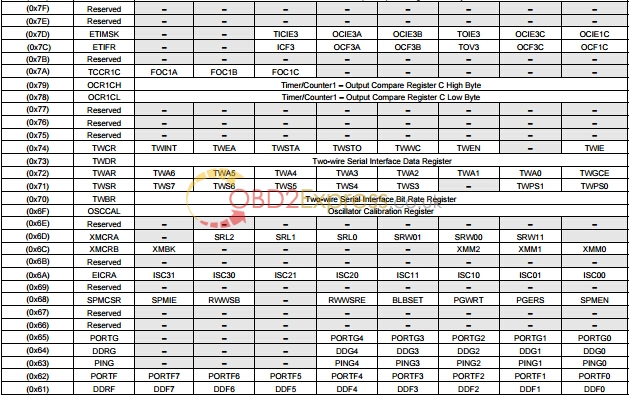

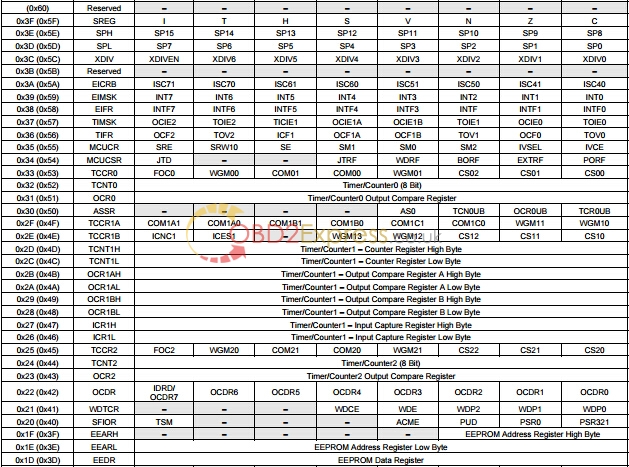

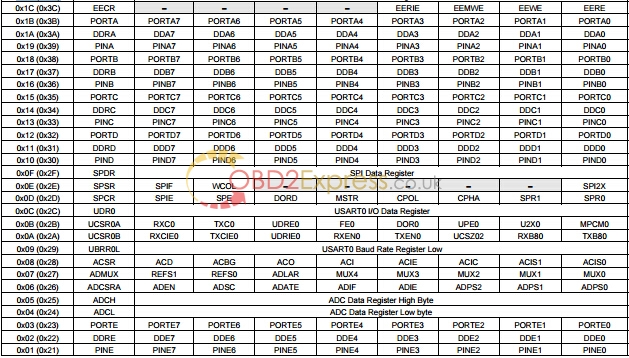

The ATmega64 chip is a highly complex microcontroller where the number of I/O locations supersedes the 64 I/O location reserved in the AVR instruction set. To ensure backward compatibility with the ATmega103, all I/O locations present in ATmega103 have the same location in ATmega64. Most additional I/O locations are added in an Extended I/O space starting from 0x60 to 0xFF (i.e., in the ATmega103 internal RAM space). These location can be reached by using LD/LDS/LDD and ST/STS/STD instructions only, not by using IN and OUT instructions. The relocation of the internal RAM space may still be a problem for ATmega103 users. Also, the increased number of Interrupt Vectors might be a problem if the code uses absolute addresses. To solve these problems, an ATmega103 compatibility mode can be selected by programming the fuse M103C. In this mode, none of the functions in the Extended I/O space are in use, so the internal RAM is located as in ATmega103. Also, the extended Interrupt Vectors are removed. The ATmega64 is 100% pin compatible with ATmega103, and can replace the ATmega103 on current printed circuit boards. The application note "Replacing ATmega103 by ATmega64†describes what the user should be aware of replacing the ATmega103 by an ATmega64.

By programming the M103C Fuse, the ATmega64 will be compatible with theATmega103 regards to RAM, I/O pins and Interrupt Vectors as described above. However, some new features in ATmega64 are not available in this compatibility mode, these features are listed below:

• One USART instead of two, asynchronous mode only. Only the eight least significant bits of the Baud Rate Register is available.

• One 16 bits Timer/Counter with two compare registers instead of two 16 bits Timer/Counters with three compare registers.

• Two-wire serial interface is not supported.

• Port G serves alternate functions only (not a general I/O port).

• Port F serves as digital input only in addition to analog input to the ADC.

• Boot Loader capabilities is not supported.

• It is not possible to adjust the frequency of the internal calibrated RC Oscillator.

• The External Memory Interface can not release any Address pins for general I/O, neither configure different wait states to different External Memory Address sections.

• Only EXTRF and PORF exist in the MCUCSR Register.

• No timed sequence is required for Watchdog Timeout change.

• Only low-level external interrupts can be used on four of the eight External Interrupt sources.

• Port C is output only.

• USART has no FIFO buffer, so Data OverRun comes earlier.

• The user must have set unused I/O bits to 0 in ATmega103 programs.

VCC

Digital supply voltage.

GND

Ground.

Port A (PA7..PA0)

Port A is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B (PB7..PB0)

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port C (PC7..PC0)

Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running. Port C also serves the functions of special features of the ATmega64. In ATmega103 compatibility mode, Port C is output only, and the port C pins are not tri-stated when a reset condition becomes active.

Port D (PD7..PD0)

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port E (PE7..PE0)

Port E is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port E output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port E pins that are externally pulled low will source current if the pull-up resistors are activated. The Port E pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port F (PF7..PF0)

Port F serves as the analog inputs to the A/D Converter. Port F also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used. Port pins can provide internal pull-up resistors (selected for each bit). The Port F output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port F pins that are externally pulled low will source current if the pull-up resistors are activated. The Port F pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PF7(TDI), PF5(TMS) and PF4(TCK) will be activated even if a reset occurs.The TDO pin is tri-stated unless TAP states that shift out data are entered.Port F also serves the functions of the JTAG interface.In ATmega103 compatibility mode, Port F is an input port only.

Port G (PG4..PG0)

Port G is a 5-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port G output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port G pins that are externally pulled low will sourcecurrent if the pull-up resistors are activated. The Port G pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port G also serves the functions of various special features.In ATmega103 compatibility mode, these pins only serves as strobes signals to theexternal memory as well as input to the 32 kHz Oscillator, and the pins are initialized to PG0 = 1, PG1 = 1, and PG2 = 0 asynchronously when a reset condition becomes active, even if the clock is not running. PG3 and PG4 are Oscillator pins.

RESET

Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table 19 on page 50. Shorter pulses are not guaranteed to generate a reset.

XTAL1

Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

XTAL2

Output from the inverting Oscillator amplifier.

AVCC

AVCC is the supply voltage pin for Port F and the A/D Converter. It should be externally connected to VCC, even if the ADC is not used. If the ADC is used, it should be connected to VCC through a low-pass filter.

AREF

AREF is the analog reference pin for the A/D Converter.

PEN

This is a programming enable pin for the SPI Serial Programming mode. By holding this pin low during a Power-on Reset, the device will enter the SPI Serial Programming mode. PEN has no function during normal operation.

![]()

Notes:

1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

2. Some of the status flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on all bits in the I/O Register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers 0x00 to 0x1F only

Posted by: OBDexpress.co.uk at

07:18 AM

| No Comments

| Add Comment

Post contains 2244 words, total size 20 kb.

March 02, 2016

Here’s the tested result of tuning chip differences between UPA-USB and Xprog-m ECU programmer. UPA USB chip tuning is good in doing MOTOROLA chip while X-prog m supports on-board and in-circuit programming of better following chips including Motorola 68HC05, 68HC08, 68HC11, 68HC(S)12 family MCU's, Texas Instruments TMS370/TMS374 family MCU's and serial EEPROM's.

UPA USB Programmer Support the following chips:..

STMicroelectronics ST62*: ST6240, ST6245, ST6249

NSC CR16*: CR16HCS5(9), CR16MCS5(9), CR16MES5(9), CR16MFS5(9), CR16MCT5/9, CR16HCT5/9

Motorola HC05*: MC68HC05B6, MC68HC05B8, MC68HC05B16, MC68HC705B16, MC68HC05B32, MC68HC05E6, MC68HC705E6, MC68HC05H12, MC68HC05L28, MC68HC05P3, MC68HC705P3*,MC68HC05X16, MC68HC05X32

Motorola HC08*: MC68HC08AS20, MC68HC08AS32, MC68HC08AS60, MC68HC08AZ32, MC68HC(9)08AZ32A, MC68HC908AZ60, MC68HC908AZ60A

Motorola HC11*: MC68HC11A1, MC68HC11A8, MC68HC11E9, MC68HC11EA9, MC68HC11E20, MC68HC11F1, MC68HC11K4, MC68HC11KA2, MC68HC11KA4, MC68HC11KG4, MC68HC11KS2, MC68HC11KS8, MC68HC11L6, MC68HC11P2, MC68HC11PA8, MC68HC11PH8

The XPROG-m supports in-circuit or on-board programming of:

Motorola 68HC05 , 68HC08, 68HC11, 68HC(S)12 , HC912, MC9S12, MC9S12X

Texas Instruments TMS370 , MPC5xx, ST10Fxx, ATmega family MCU's

serial EEPROM's

XPROG-m programmer is fully upward-compatible hardware with XPROG programmer and have many additional features.

All supported devices are divided into "Software authorization" licenses. You can obtain authorization license only for these devices you are interested in.

NOTE:

UPA : Cannot read secured mcu / Xprog-m: Can read secured mcu

UPA : must have knowledge to use with processor / Xprog-M: Must be good in soldering / desoldering

Posted by: OBDexpress.co.uk at

09:13 AM

| No Comments

| Add Comment

Post contains 217 words, total size 3 kb.

32 queries taking 0.1933 seconds, 119 records returned.

Powered by Minx 1.1.6c-pink.